Hierarchical and Incremental Design Rule Checker

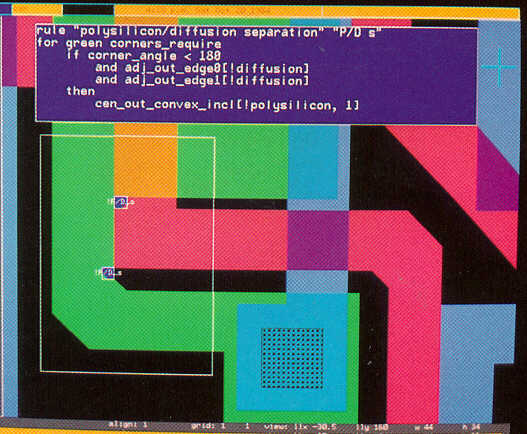

| This powerful layout design rules check program is compatible with all IC processes. Design rule violations are graphically highlighted in color. Design and technology contraints are user configurable through the use of a proprietary Design Rule Compiler. This checker employs a sophisticated corner-based algorithm that is both fast and accurate. It is a hierarchical checker, checking only the first instance of a repeated cell within a design hierarchy, allowing tremendous speed realtive to conventional "flat" DRC programs. It is also incremental, checking only new or altered cells within the specified area. |

| Leo45 Leo 45 checks the geometry of a mask layout for design rule violations. It identifies problems such as minimum-spacing viloations, minimum-width violations, parallel edge-spacing violations, and malformed-circuit constructions. It labels the violations that it finds in the physical layout file (".phl") that it checked, allowing you to correct the violations in context. Leo45 checks geometries that use 45 and 90 degree angles. |

|

| Leo45: Fully hierarchical incremental geometric design rule checking for any technology. Interactive from the physical layout editor. |

Return